According to the theory of relativity, time can also be lengthened and shortened, but it requires huge energy to support you to reach a high speed comparable to the speed of light. This is easy to say, you and I understand in my heart, it is estimated that we will not see such a scene in our lifetime...

Back in the field of programmable logic devices, with the adoption of 65nm, 40nm, and even the current 28nm deep submicron process, manufacturers have produced larger and more complex FPGA devices. While users are delighted by the ever-increasing functionality of FPGAs and the declining unit cost, they are also distressed by the relatively low development efficiency associated with the performance lag of related EDA software, especially for high-capacity FPGA chips. The compilation time of 10 to 20 hours can be described as resentful. When I faced a front-line FPGA engineer many times, I heard such a similar statement: If the compile time can be pressed, it will be fine!

Altera can't really compress time, but we can change the "speed"! Starting with the version a few years ago, the Quartus 2 software incorporates a new technology, or a new design flow: Incremental CompilaTIon. It is a new tool given by ALTERA to solve the problem that the compilation time of large-capacity FPGA design is too long! You, understand it?

Incremental compilation principle and process

The principle of incrementally compiling QIC is easy to understand: for a complex design, it is necessary to do a certain functional division, which is implemented by different sub-function modules. Then, when the design enters the later stage of maturity, in the design version compiled twice before, there will be a large part of the circuit logic is the same (no modification), if it can be reused in the previous compilation, the previous compilation is repeated. The uncompiled part of the compilation result, that is, the layout and routing information of the corresponding part, can save the layout time consumed by this part of the logic, thereby greatly shortening the compilation time of the entire design. Of course, smart readers can think of this kind of compilation, in addition to shortening the compile time, can also support many other purposes, such as IP design delivery, team development, without changing the normal design results into the debug interface. These are really functions that ALTERA incremental compilation can do, but in this article we only explain the role of QIC in reducing compilation time.

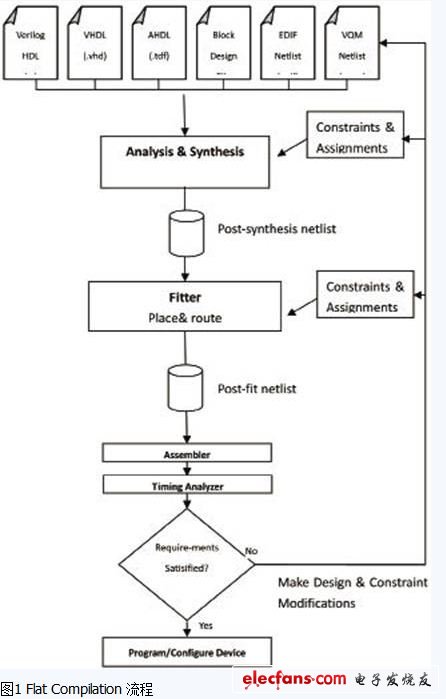

Although the incremental compilation principle is simple, it is implemented in the EDA software of the FPGA, but it is a complicated system engineering. It is not simply adding a function module to the software, but changing and enhancing the compilation process flow in many ways! Please compare the two figures in Figure 1 and Figure 2: Figure 1 is the traditional FPGA compilation process (Altera name: Flat compilaTIon), Figure 2 is a schematic diagram of the incremental compilation process. It is easy to find that the incremental compilation process is much more complicated. It not only introduces some new concepts, such as design partition (parTITIon), partition synthesis netlist, partition layout/router netlist, etc., but also adds a new processing stage. -- Partition merging, and improvements to the Analysis & Synthesis and Fitter stages, adding many specific operations for partitioning.

After several years of research and practice, Quartus II's incremental compilation has been gradually improved, both in terms of operability, robustness, and in reducing the effect of compile time. Among the several customer projects that the author participated in, through the implementation of QIC, they achieved a compilation time savings of about 50%, which greatly improved the development efficiency of customers. Below, I will combine the experience of these practical projects to introduce how to use QIC to effectively shorten the design compilation time.

Barium titanate lead-free piezoelectric ceramics are important basic materials for the development of modern science and technology, which was widely used in the manufacture of ultrasonic transducers, underwater acoustic transducers, electroacoustic transducers, ceramic filters, ceramic transformers, ceramic frequency discriminators, high voltage generators, infrared detectors, surface acoustic wave devices, electro-optic devices, ignition and detonation devices, and piezoelectric gyroscope and so on.

Application: military, ocean, fishery, scientific research, mine detection, daily life and other fields.

Piezo Disc,Piezo Rod,Lead Free Piezo Rods,Lead Free Piezo Discs

Zibo Yuhai Electronic Ceramic Co., Ltd. , https://www.yhpiezo.com