The Ćuk DC-DC converter designed by Dr. Ćuk is known for its low input and output ripple currents and can be used as a buck-boost converter. This design example shows a new converter architecture for Dr. Ćuk, a resonant converter that can resonate with a very small number of inductors and large capacitors even at relatively low frequencies (eg, 50 kHz). Dr. Ćuk tends to maintain a low switching frequency, but increasing the frequency can achieve a faster transient response with a smaller LC value.

Many engineers are aware of Dr. Slobodan Ćuk (pronounced like chook) who is the designer of the Ćuk DC-DC converter architecture, which is known for its low input and output ripple currents and can also be used as a buck-boost device. use.

So recently when I noticed that Dr. Ćuk has released a new converter architecture, my interest was immediately adjusted.

I have been in constant contact with the good doctor, but I am not very clear about his new design. The prototype seems to have been completed, but the details have not been revealed.

This design is considered to be a resonant converter that can still resonate with large capacitors through a very small number of inductors (or even just PCB traces) even at relatively low frequencies (eg 50 kHz).

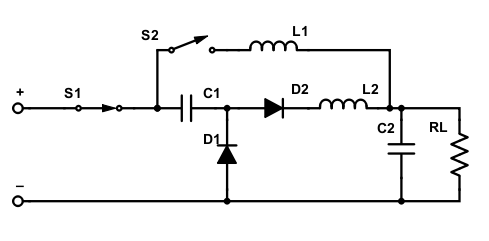

Figure 1: Resonant buck converter and charge pump proposed by Dr. Ćuk.

I find that the current circuit description is a bit difficult to understand (this does not necessarily mean that my ability is not enough), the following is just some of my rough understanding of the design.

If you ignore the inductor (replace it with a short circuit), it is basically a charge pump that runs at 2:1 ratio.

It is envisaged that the circuit is more or less in equilibrium and the switch is shown in Figure 1: The input voltage will be divided between C1 and C2. When the switch is toggled, C1 will be in parallel with C2 (via S2 and D1), transmitting some power to supplement C2.

By using an inductor, each charge pump (CP) phase is half the resonant period. This reduces the current spikes that occur in standard CP designs, and can achieve duty cycle control of the output voltage without loss of efficiency (because the inductance reduces the charge transfer rate). I think that the control circuit must also take a burst mode to keep the output voltage from rising at low loads because in the charge transfer phase, the energy of L2 will continue to be transferred into the capacitor.

D1 and D2 can be actual diodes if they do not care about loss, but in most cases they should be synchronous switches. Dr. Ćuk pointed out that in this case, replacing the D2 FET may require blocking the current during an open circuit, just like a diode, but its source replaces the N2 FET of the D2 cathode (as shown in a schematic circuit diagram of Dr. Ćuk. (shown) will point a body diode in the wrong direction. A back-to-back FET may be necessary, but with the right control circuitry, I think the source may be on the left.

Through this design, I believe that my analytical capabilities have been improved, but if you think that my analysis is not correct, please share your understanding of and understanding of the circuit. Is this a reminder that I need to improve simulation skills? We will wait and see.

Dr. Ćuk seems to prefer to keep the switching frequency low, but I think there is no reason not to increase the frequency so that a faster transient response can be obtained with a smaller LC value (but this will increase switching losses). What are the specific benefits? Let us look at some examples:

50kHz: 1000μF, 10nH 500kHz: 22μF, 4.6nH 2MHz: 6.8μF, 1nH

Sometimes square root operations are really useful.

So what do you think about the potential value of this design?

push switch socket, wall swich socket, high quality switch socket

Guangdong Shunde Langzhi Trading CO., Ltd , https://www.langzhielectrical.com