A notable feature of dynamic memory is that the stored data is volatile and must be refreshed within a specified time. In this system, the timer 1 timer interrupt of the 8031 ​​is used to refresh the DRAM. The program for timing interrupt refresh is as follows:

When refreshing, set T1 first. In the fetch cycle of DEC 70H statement, 8031 ​​fetches the instruction from the external program memory EPROM, PSEN is valid. At this time, Tl is high, making RAS valid. At the same time, the EPROM address of the store instruction is also sent. On the address line, the lower 9 bits are also sent to the DRAM as row addresses to achieve DRAM-line refresh. Since the DEC 70H statement operates on the internal RAM, there will be no other addresses on the address line. The OlOOH strip DEC 70H statement (0200H bytes) can be executed continuously, which can refresh the 1 MB DRAM (1 MB DRAM needs 9 Bit refresh address).

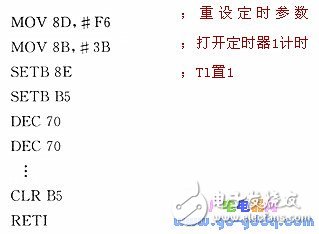

Enter the interrupt program, immediately reset the timer 1 parameter and turn on the timer to make the timing continuous. The count input signal of Timer 1 is derived from the internal clock pulse and the count rate is 1/12 of the oscillator frequency. If a 12 MHz quartz crystal is used as the oscillator, the counting rate is 1 MHz. When the setting parameter is FFFFH - F63BH - 09C4H, the timing refresh period is 2.5 ms. At present, the general 1 MB DRAM refresh cycle is 16 ms, so the timing parameter value can be set larger.

Data buffer management

The management of the data buffer can be done in a circular queue. The main program sends data to the host computer, and judges the queue according to the head and tail pointer positions of the queue and the front and rear flags, and uses the interrupt to receive new data and refresh the DRAM. This side-by-side, side-by-send operation keeps the buffers efficient. The interrupt source level of the refresh DRAM should be higher than the interrupt request of the received data to ensure that the DRAM is refreshed on time.

Coin Cell Holders

Coin Cell Holders

ATKCONN ELECTRONICS CO., LTD , https://www.atkconn.com